### **Comparison of Memory Access Strategies in Multi-core Platforms using MAST**

Juan M. Rivas<sup>1</sup>, J. Javier Gutiérrez<sup>2</sup>, Julio L. Medina<sup>2</sup> and Michael González Harbour<sup>2</sup> <sup>1</sup>PARTS Research Center, Université Libre de Bruxelles (Belgium) - <sup>2</sup>Software Engineering and Real-Time, University of Cantabria (Spain)

<sup>1</sup>jrivasco@ulb.ac.be, <sup>2</sup>{gutierjj, medinajl, mgh}@unican.es

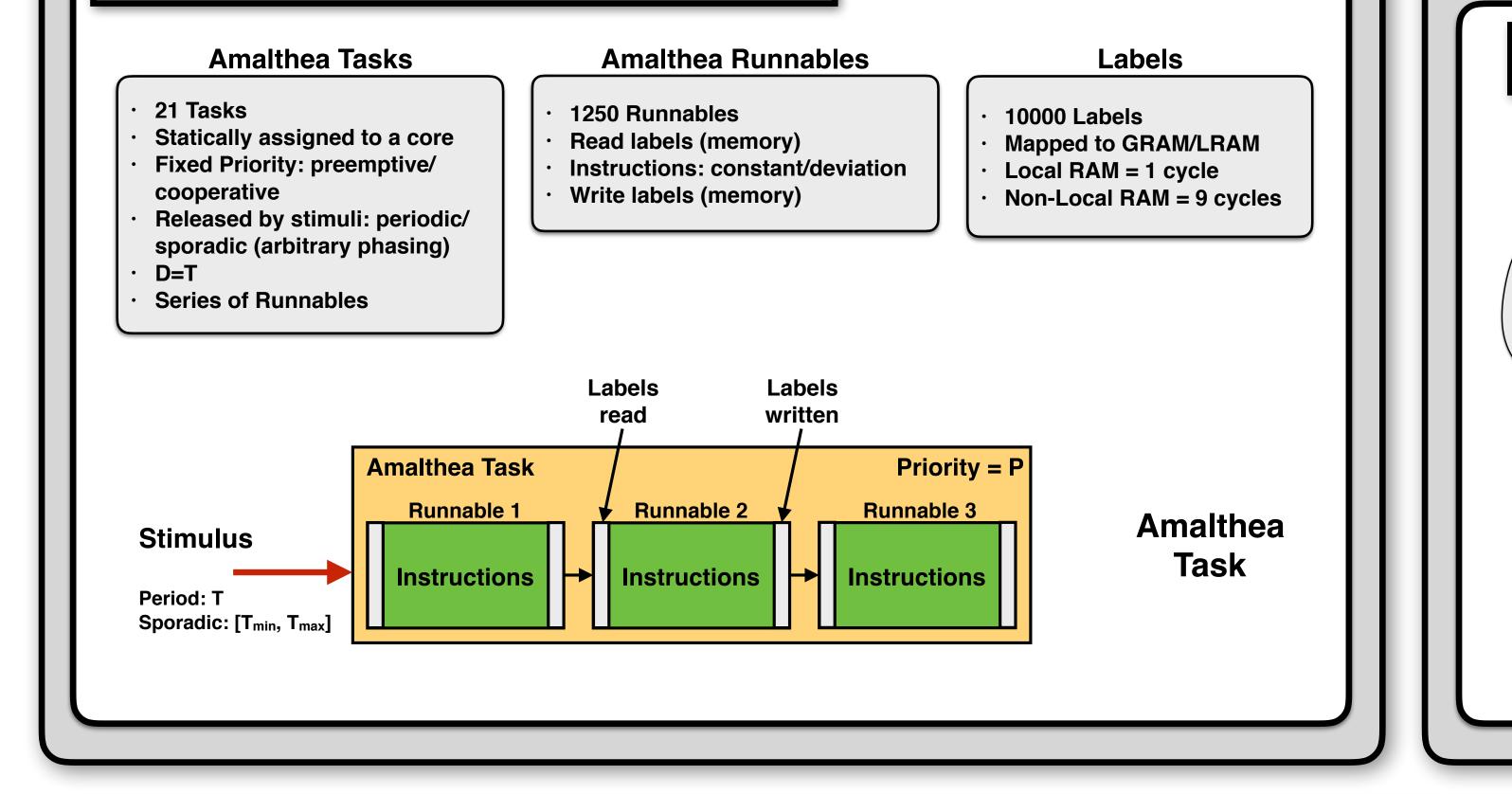

## The Challenge

Challenge: To calculate latencies in an engine management system

| CORE0 CORE1 CORE2 CORE3 |        | Memory access times (cycles) |       |        | )     |      |

|-------------------------|--------|------------------------------|-------|--------|-------|------|

|                         |        | LRAM0                        | LRAM1 | LRAM2  | LRAM3 | GRAM |

|                         | CORE0  | 1                            | 9     | 9      | 9     | 9    |

|                         | CORE1  | 9                            | 1     | 9      | 9     | 9    |

|                         | CORE2  | 9                            | 9     | 1      | 9     | 9    |

| CROSSBAR                | CORE3  | 9                            | 9     | 9      | 1     | 9    |

| 200 MHz system-wide     | FIFO a | arbitı                       | ratio | n at I | mem   | orie |

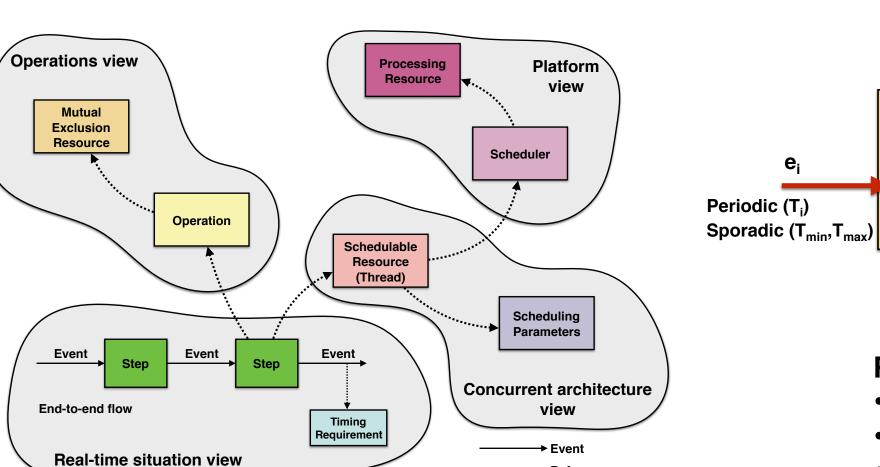

# **Approach: RTA with MAST**

## **MAST Tool**

Tool to model, analyze and optimize real-time systems

#### **Open source, available at <u>mast.unican.es</u> (Windows and Linux)**

| Schedulabilty<br>analysis tools                                                                                                                                | Optimization tools                                                                                                                | Other tools                                                                                                   | Support                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Holistic</li> <li>Offset-based</li> <li>Offset-based slanted</li> <li>Offset-based w/<br/>precedence</li> <li>Offset-based brute<br/>force</li> </ul> | <ul> <li>Simulated annealing</li> <li>UD</li> <li>ED</li> <li>PN</li> <li>NPD</li> <li>EQS</li> <li>EQF</li> <li>HOSPA</li> </ul> | <ul> <li>Simulator</li> <li>Sensitivity analysis</li> <li>Graphical editor</li> <li>Results viewer</li> </ul> | <ul> <li>Shared resources</li> <li>Multipath e2 flows</li> <li>Sporadic and Polling<br/>Servers</li> <li>FP+EDF scheduling</li> <li>Networks (AFDX, CAN)</li> <li>Partitioned systems</li> <li>Generator (GEN4MAST)</li> </ul> |

Reference

MAST model for analysis

**Results from response-time analysis:**

- Worst-case Local response time: r<sub>ii</sub>

- Worst-case Global response time: R<sub>ij</sub>

- Best-case response times: r<sup>b</sup><sub>ii</sub>, R<sup>b</sup><sub>ii</sub>

#### **Approach: RTA with MAST**

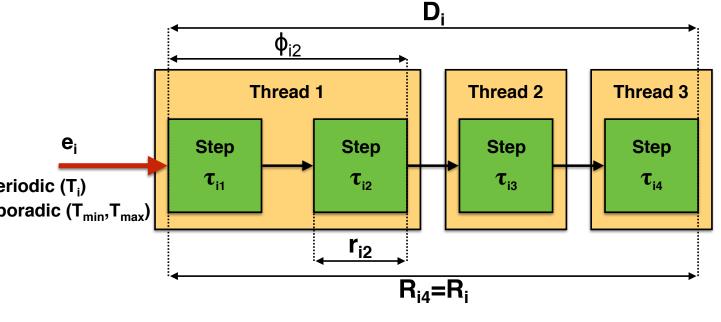

| Amalthea to MAST transformation |                                      |   |                       | 1. stores medel of data flows omeng ner conceptive runnables |  |  |

|---------------------------------|--------------------------------------|---|-----------------------|--------------------------------------------------------------|--|--|

|                                 |                                      | ļ | Event-chains          | Latency model of data flows among non consecutive runnables  |  |  |

|                                 | ······                               |   | Event-chains crossing | different tasks                                              |  |  |

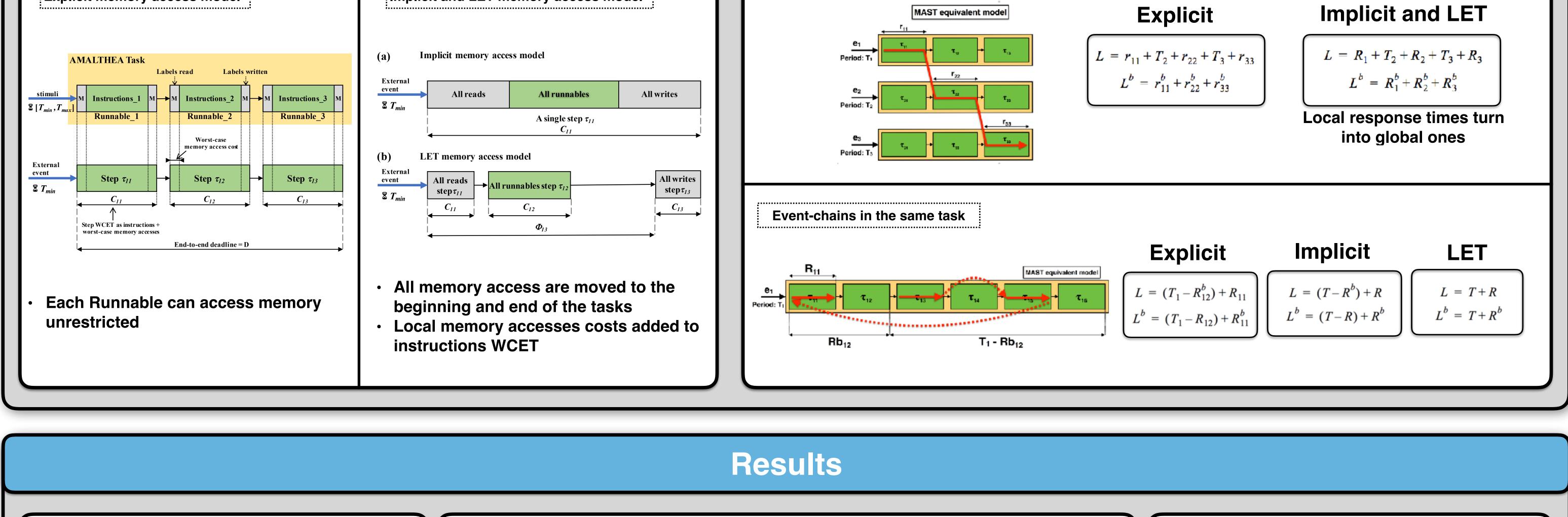

| Explicit memory access model    | Implicit and LET memory access model |   |                       |                                                              |  |  |

| Considerations                   | Event-chain latencies                                                                                               | Conclusions |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------|

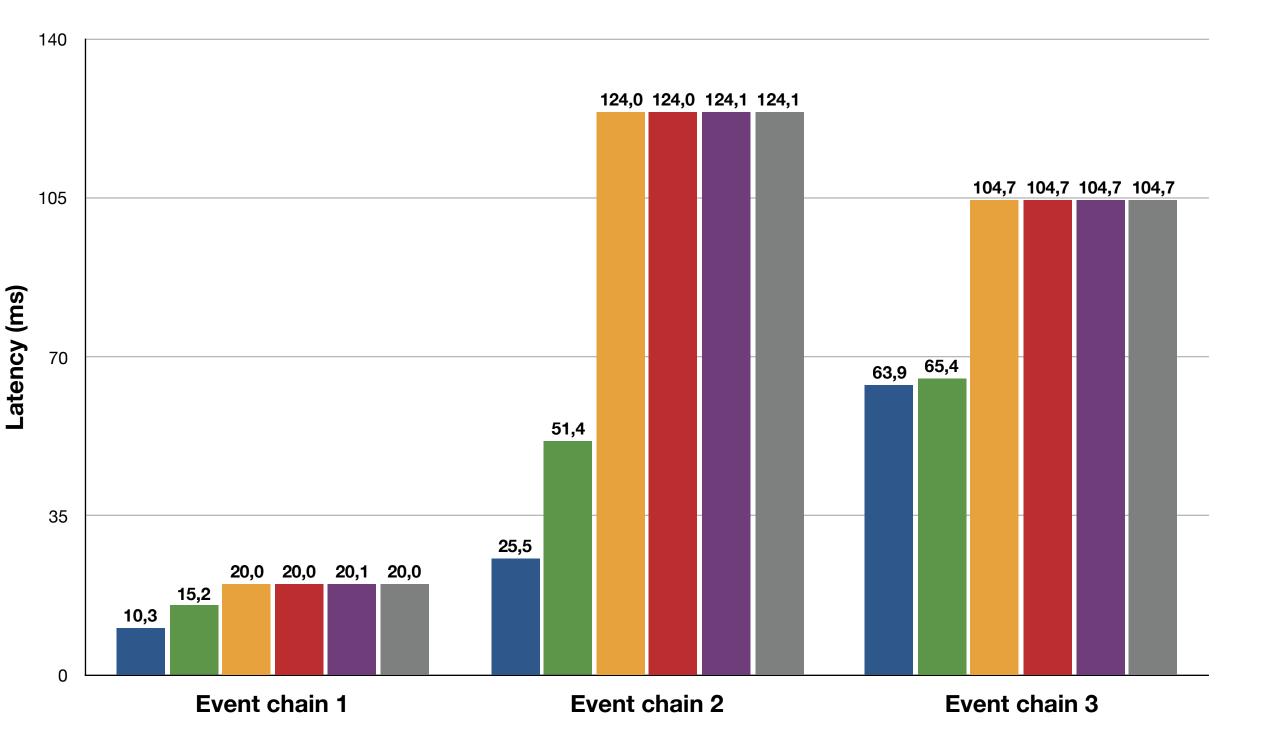

| Clock speed increased to 300 MHz | 🔳 Explicit 📕 Implicit 📕 LET-Dynamic (2 bands) 📕 LET-Dynamic (3 bands) 📕 LET-Static (2 bands) 📕 LET-Static (3 bands) |             |

None of the strategies is a clear winner No solution can reduce jitter and latencies at the same time

Implicit model has similar latencies than **Explicit for the tasks and higher latencies** for the event chains without getting a reduction of jitter

Penalty to keep data consistency

LET has a good control of jitter at the cost of a significant increase of latencies for both tasks and event chains.